Piirivalmistaja Xilinx laajentaa nykyisen piiritarjontansa lisäksi datakeskuksiin. Yrityksen toimitusjohtaja Victor Peng esitteli uusia visioita ja strategiaa äskettäin. Niissä korostuvat aiempien sovellusten lisäksi kiihdytetty ACAP-laskenta. Yritys lupaa pysyä silti myös nykyisillä FPGA-piirien sovellusalueilla.

Xilinxin uusi Adaptive Compute Acceleration Platform (ACAP) on yrityksen mukaan merkittävä teknologinen elementti yrityksen uuden vision toteuttamisessa. Se on integroitu heterogeeninen laskentatapa, jota voidaan muuttaa laitteistokohtaisesti sopeutumaan monenlaisten sovellusten ja työmäärän tarpeisiin.

ACAP sopii erinomaisesti esimerkiksi laajojen sovellusten nopeuttamiseen suuren datan ja tekoälyn aikana. Näihin kuuluvat: videokoodaus, tietokanta, tiedon pakkaaminen, haku, AI-päättely, genomiikka, konenäkö, laskennallinen tallennus ja verkon kiihdytys.

”Tämä on tärkeä tekniikan murros teollisuudelle ja merkittävin tekninen saavutus FPGA: n keksimisen jälkeen”, mainostaa ACAP-ratkaisuaan Xilinxin toimitusjohtaja Victor Peng.

Ensimmäinen ACAP-tuoteperhe, koodinimeltään Everest, valmistetaan TSMC:n seitsemän nanometrin prosessilla. Ensimmäisiä tuloksia luvataan vielä tänä vuonna ja piiritoimituksiin Xilinx pyrkii vuonna 2019.

Tulevien Everest-piirien luvataan saavuttavan 20 kertaisen parannuksen syvien hermoverkkojen laskennassa verrattuna uusimpiin Xilinxin16 nanometrin Virtex VU9P FPGA-piireihin.

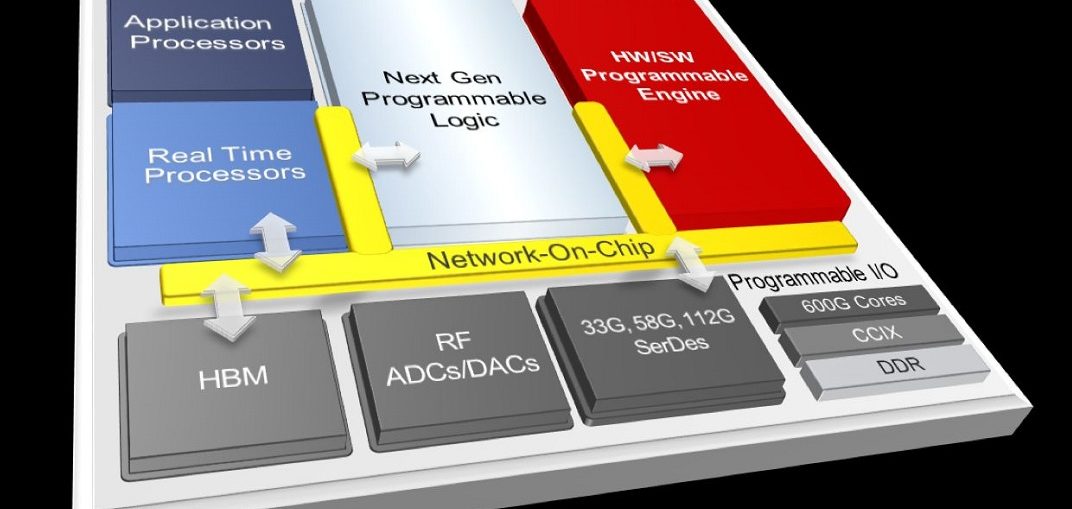

Everestin luvataan tarjoavan entistä parempaa suorituskykyä ja suorituskykyä wattia kohti verrattuna tämän päivän CPU-, GPU- ja FPGA-tekniikoihin. ACAP:n ydin on uuden sukupolven FPGA-verkko, jossa on hajautettu muisti ja laitteisto-ohjelmoitavat DSP-lohkot, moniportainen SoC ja yksi tai useampi ohjelmoitava laitteisto.

ACAP:ssä on myös integroitu ohjelmoitava I/O-toiminto, joka koostuu ohjelmoitavista laitteistohallintaohjaimista, kehittyneestä SerDes-tekniikasta, suuren kaistanleveyden muistim HBM-rajapinnasta ja liitynnöistä RF-DC/DAC-järjestelmästelmiin. Ohjelmistokehittäjät voivat ohjelmoida ACAP-pohjaisia järjestelmiä käyttämällä C / C ++, OpenCL- ja Python-työkaluja. ACAP voidaan ohjelmoida myös RTL-tason FPGA-työkaluilla.