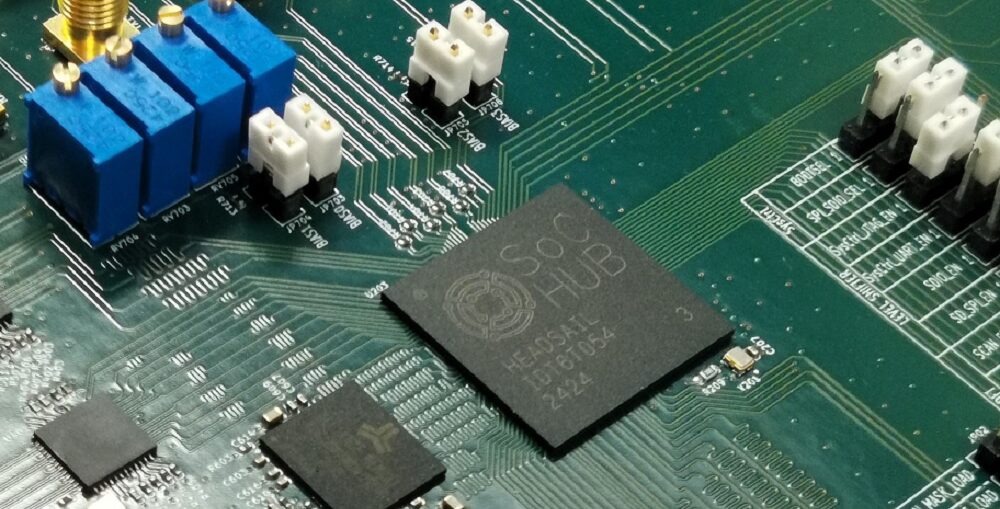

Suomalainen RISC-V-ytimen sisältävä kolmannen sukupolven järjestelmäpiiri Headsail on päässyt jo käytännön testeihin. TSCM:ssä Taiwanissa valmistetun piirin takana ovat Tampereen yliopiston ja seitsemän suomalaisyrityksen SoC Hub -suunnitteluyhteisö.

Uusin Headsail-järjestelmäpiiri on projektikonsortion kehittämistä kolmesta piireistä kaikkein monimutkaisin. Se sisältää 330 miljoonan transistorin lisäksi neliytimisen 64-bittisen RISC-V-alijärjestelmän ja tekoälykiihdyttimen sekä yrityskohtaista IP-osuuksia.

’’Järjestelmäpiiriä rakennettiin lisäämällä sisältöjä aiemmin kehitettyihin piireihin sekä uudelleenkäyttämällä uuden piirin tarkoituksiin parhaiten sopivia lohkoja’’, kertoo tietotekniikan professori Timo Hämäläinen Tampereen yliopistosta.

Uusimman Headsailin suunnittelu aloitettiin loppuvuodesta 2022 samaan aikaan, kun projektin toista järjestelmäpiiriä viimeisteltiin tuotantoon lähettämistä varten.

Suunnittelu oli valmis elokuussa 2023, ja piiri lähetettiin Taiwaniin tuotantoon (tape-out). Valmiit vielä koteloimattomat piirit saatiin Tampereelle kolme kuukautta siiten. Hieman myöhemmin piireille toteutettiin kustomoitu kotelo, johon aikaa kului lopulta noin puoli vuotta, ja valmiit koteloidut piirit saatiin konsortion haltuun heinäkuussa 2024.

Testauksen ensimmäisessä vaiheessa havaittiin onneksi lopulta, että siru on sähköisesti toimiva. Kaikki alijärjestelmät voitiin kytkeä päälle ja ne ovat yhdistettävissä. RISC-V -prosessorialijärjestelmä suoritti onnistuneesti ensimmäisen ”Hello World” -ohjelman jokaisella ytimellään, kertoo testausta valvova Arto Oinonen Tampereen yliopistosta.

Projektitiimi jatkaa edelleen piirien perusteellisempaa testausta sekä piiriin perustuvien demojärjestelmien rakentamista. Niitä tulevat olemaan esimerkiksi tekoälysovellukset, ääniprosessointi ja reaaliaikaiset kriittiset viestintäsovellukset.

Lisää: Soc Hub (LINKKI) ja aiemmat SoC Hubin piirisuunnittelua käsitelleet uutiset (LINKKI).

Kuva: Kortilla oleva Headsail-piiri on suunniteltu vuonna 2020 käynnistyneessä Business Finlandin rahoittamassa co innovation -projektissa. Siihen ovat osallistuneet Tampereen yliopiston lisäksi Nokia, CoreHW, VLSI Solution, Wapice, Hiab, Procemex ja TTTEch Flexibilis.