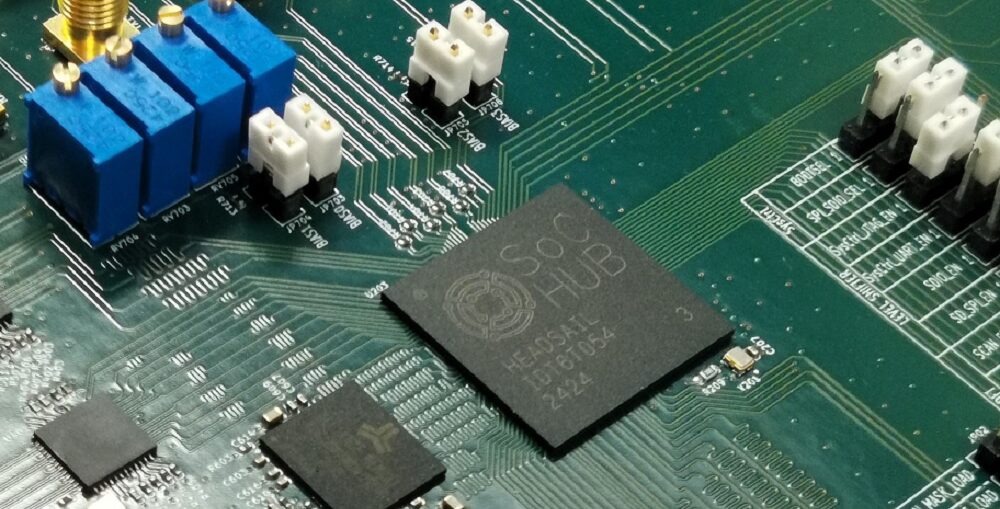

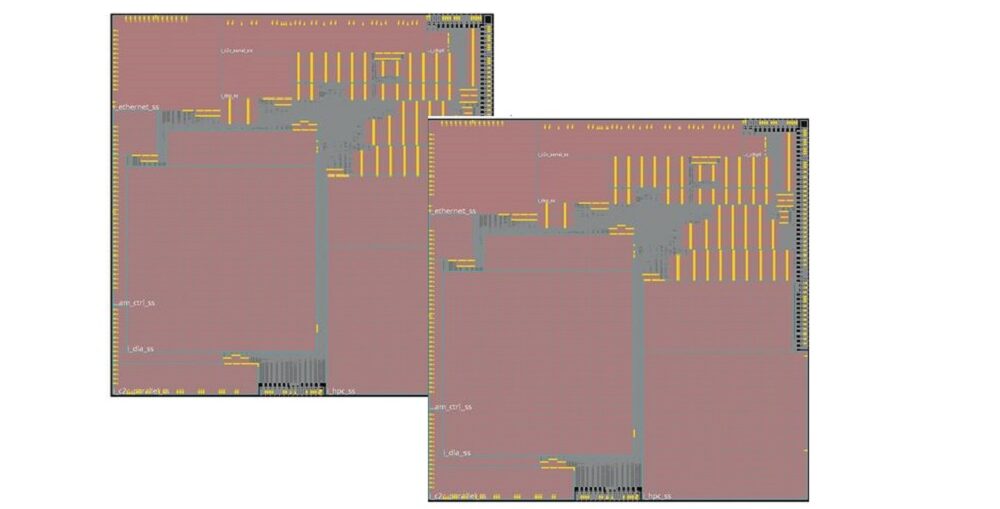

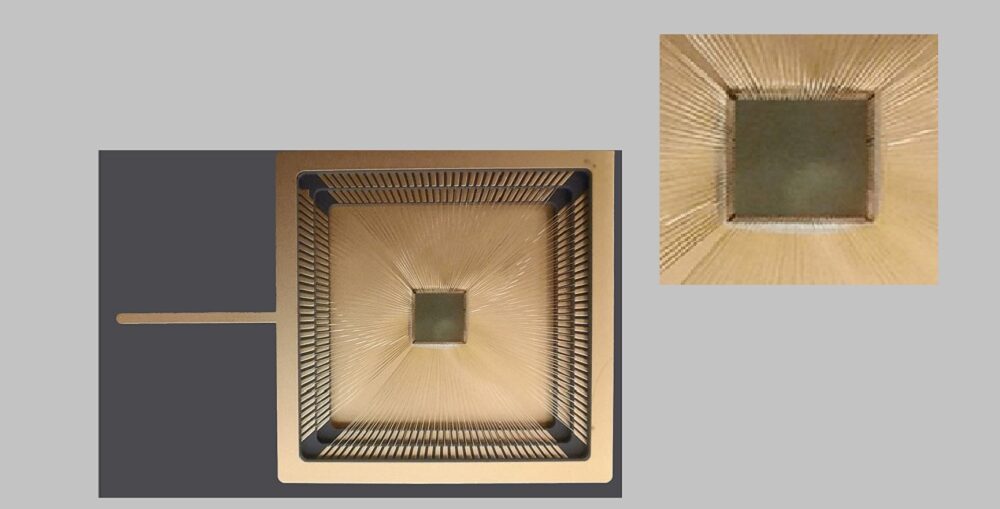

Suomalainen RISC-V-ytimen sisältävä kolmannen sukupolven järjestelmäpiiri Headsail on päässyt jo käytännön testeihin. TSCM:ssä Taiwanissa valmistetun piirin takana ovat Tampereen yliopiston ja seitsemän suomalaisyrityksen SoC Hub -suunnitteluyhteisö.

Tag: Risc-V

64-bitin RISC-V-ohjaimella kätevä FPGA-kehityskortti

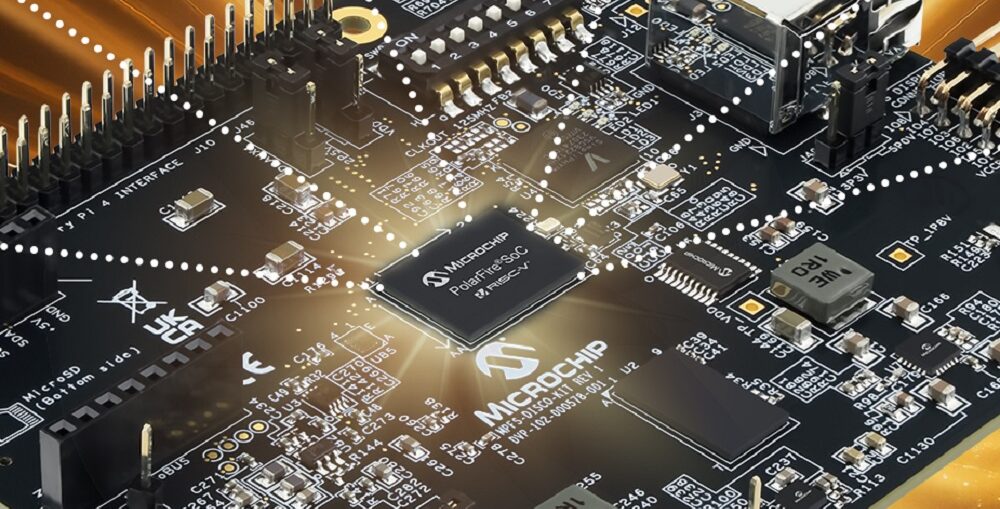

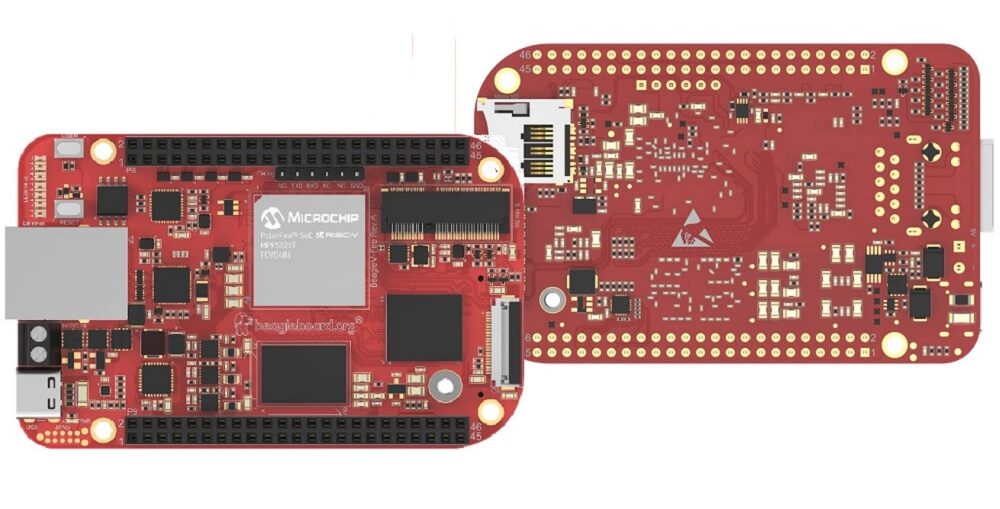

Sulautettua elektroniikkaa kehittävät näkevät uuden avoimen lähdekoodin RISC-V-suoritinalustan entistä kiinnostavampana. Nopeuttaakseen alueen kehitystä siruvalmistaja Microchip on esitellyt pienen kehitysalustan, joka yhdistää yrityksen ohjelmoitavan FPGA-piirin 64-bittisen RISC-V-arkkitehtuurin kanssa.

Pieni RISC-V-korttitietokone FPGA-ohjelmoinnilla

Tamperelainen RISC-V-piiri tuotantoon

Soc Hubin RISC-V-yhteispiiri pian koekäyttöön

ARMin kisaajalle päivitettyjä kehitystyökaluja

Mikroprosessorien kehitysjärjestelmien tekijät ovat entistä kiinnostuneempia tarjoamaan Armin lisäksi uutta RISC-V-arkkitehtuuria. Uusimpana saksalainen Segger ja ruotsalaistaustainen IAR ovat tuoneet tarjolle työkaluistaa päivitetyt versiot RISC-V-ratkaisujen kehittämiseen. Kaupallisten tuotteiden lisäksi tarjolla on tosin myös avoimen lähdekoodin RISC-V-kehitystyökaluja.

RISC-V vahvistuu uutuuspiireillä

Berkeleyn yliopistossa kehitetty avoin RISC-V-prosessoriarkkitehtuuri on saanut koko ajan uusia tukijoita. Erityisesti RISC-V on kerännyt suosiota sulautetuissa ohjainpiirityyppisissä sovelluksissa juuri muunneltavuutensa ansiosta. Uusimpana mukaan on lähtenyt Renesas uudella RZ/Five-piirisarjallaan.

Uuden ajan supersuorittimet: ARMv9 ja muu kisaajat

UUSITEKNOLOGIA 2021 SPECIAL ARM on maailman suosituin RISC-prosessoriarkkitehtuuri, jota käytetään laajalti kännyköiden ja pientietokoneiden lisäksi sulautetuissa järjestelmissä. Uusin on 64-bittinen ARM v9. Samalla kilpailijat virittelevät omia osin kilpailevia versioitaan. Tässä laaja erikoisartikkeli linkkeineen.

Opiskelijat koodasivat avoimen RISC-V-prosessorin

Aalto-yliopiston mikroelektroniikan opiskelijat toteuttivat kesällä RISC-V -mikroprosessorin laitteistokuvauksen ja on nyt julkaissut sen avoimesti verkossa. ”Työ perustuu Berkeleyn yliopistossa kehitettyyn avoimeen RISC-V-prosessoriarkkitehtuuriin”, kertoo Berkeleyssa itsekin työskennellyt, opiskelijoiden työtä ohjannut vanhempi yliopistonlehtori Marko Kosunen.